关于HSDIO延迟超过100%

主要软件:

主要软件版本: 1.5

主要软件修正版本: 1.5

次要软件: Digital Waveform Editor

硬件: Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6542, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6551, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6552, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6561, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6562, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6541, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6542, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6551, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6552, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6561, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6562, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6541

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: NI-HSDIO设备(654x, 655x, 656x)提供了数据线传输上的数据延迟功能。然而可编程的延迟最大值是100%的时钟周期。那如何能够使其延迟超过100%以兼容实时硬件的应用。

解答:

在数据延迟超过100%的情况下,比较波形可以被以2:1的插值重采样。这将重复每个采样周期,从而增加了一个看似“自然”的100%波形。

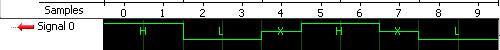

例,如果在比较波形中需要一个延迟124%波形:

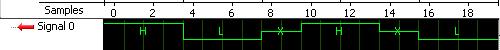

可以先插值2:1,这样每个采样都被重复了,得到了以下的波形:

这样每个采样都增加了一个100%延迟的波形。然后再用这个波形,通过程序使其延迟24%,这样最终可以得到一个延迟124%的波形。

相关链接: Knowledge Base 42JET3JQ: Per Cycle Tristate Programming with NI-HSDIO

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 10/23/2006

最近更新: 08/30/2011

文档编号: 42MATJD3