なぜRIOデバイスセットアップのデバイス設定がグレーアウトしているのでしょうか。

使用ソフトウェア: Driver Software>>NI-RIO

使用ソフトウェア・バージョン: 15.0

使用ソフトウェア・バージョンに特化: N/A

二次のソフトウェア: N/A

ハードウェア: CompactRIO

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

問題:

RIOデバイスセットアップによってデバイス設定を変更しようとしたところ、グレーアウト(Grayout)してしまいます。なぜデバイス設定タブがグレーアウトしているのでしょうか。

解決策:

一部のFPGAターゲットでは、再起動時に自動ロードと電源投入時に自動ロードの設定がないために設定項目が表示されません。

一部のFPGA ターゲットには、FPGA VI を保存できるフラッシュメモリが搭載されています。ホストコンピュータからこのフラッシュメモリにビットファイル(.lvbitx ファイル)をダウンロードしておくと、FPGA ターゲットは、起動時または再起動時にビットファイルを自動的にロードおよび実行できます。

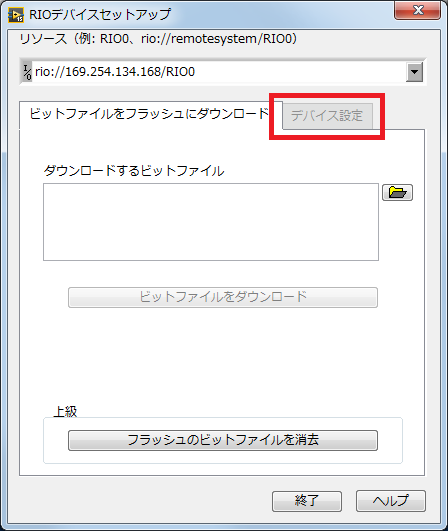

Zynq ベースのデバイスでは、図1 のように、「デバイス設定」タブがグレーアウトされているため、設定を行うことができません。

図1. Zynq ベースデバイスで「デバイス設定」タブがグレーアウト状態

メモ: 再起動時に自動ロードは電源が投入されている間にデバイスが再起動(リセット)された時に自動ロードされます。電源投入時に自動ロードの設定は電源が初めに投入された時のみ自動ロードされる設定です。

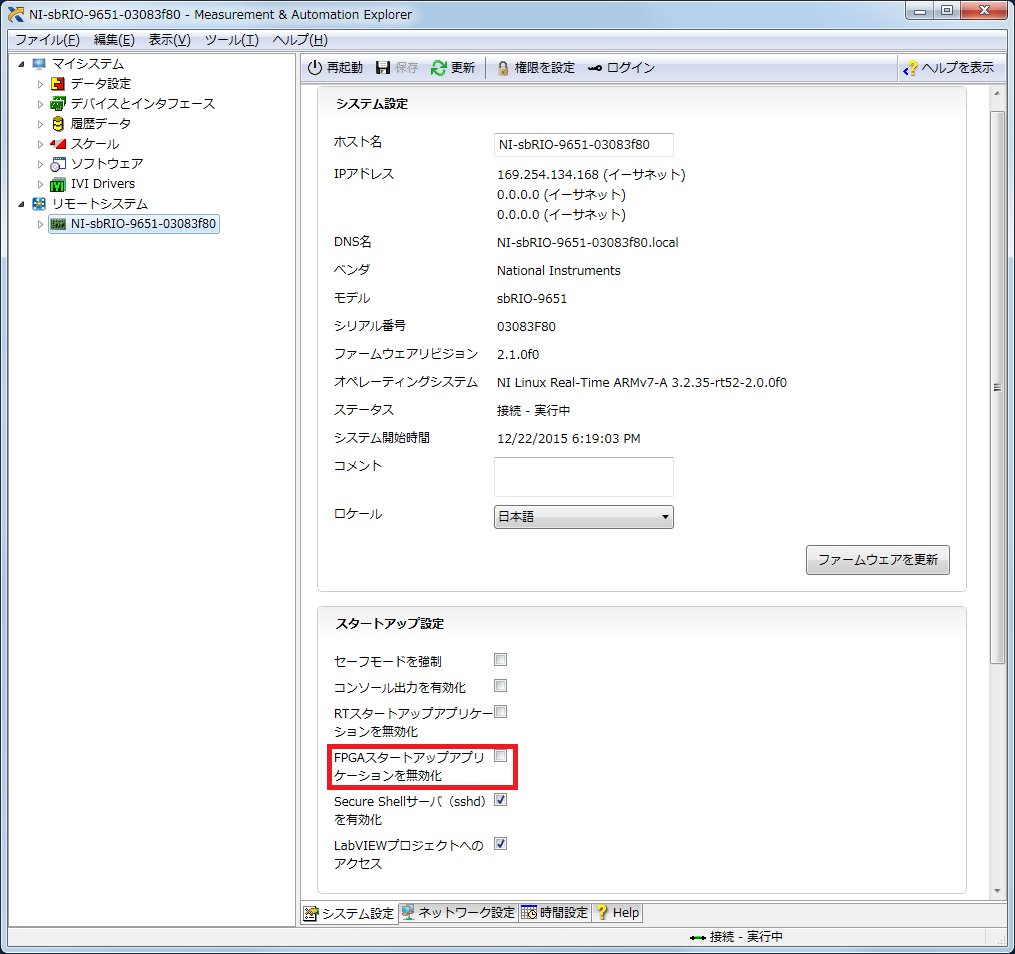

Zynq ベースのデバイスでは、電源投入時およびデバイスの再起動時に自動実行されるように設定になっており、こちらの設定を有効にするか無効にするかのみが選択できます。

図2. FPGA スタートアップアプリケーションを無効化

メモ:Zynq ベース以外のFPGA デバイスでは、電源投入時以外はFPGA を実行したまま、Real-Time OS を再起動する事ができます。Zynq ベースのデバイスでは、CPU とFPGA が1つのチップに統合されています。そのためZynq ベースのデバイスを再起動するとFPGA も一緒にリセットされます。これまでのように電源投入時以外にFPGA がリセットされないようにするには、デバイスをリセットせずに実行ファイルを再起動させる必要があります。詳しくは技術サポートデータベース 6C1CTQVQ: Restarting a cRIO-906x or myRIO Resets and Clears the FPGA and Returns the I/O to a Default Stateをご参照ください。

関連リンク: 技術サポートデータベース 4P7IJ4MO: FPGA VI をシステム起動時に実行させる方法

技術サポートデータベース 4P7IJ4MO: How Can I Have My FPGA VI Run At Boot?

技術サポートデータベース 32SDRDUL: NI RIOデバイスではどのXilinx FPGA チップが使用されていますか?

添付:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

報告日時: 03/24/2016

最終更新日: 08/08/2016

ドキュメントID: 77N7PACD