¿Por qué hay un retraso en los datos que adquiero con dispositivos DSA?

Hardware: PXI/CompactPCI>>Controllers

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

Problema:

Cuando utilizo un disparo digital en mi dispositivo de adquisición de señales dinámicas (DSA por sus siglas en inglés), noto que existe un retraso antes de que se adquieran los primeros datos. Por ejemplo, si adquiero de la misma señal con una tarjeta de la serie M y un dispositivo DSA de forma simultánea, parece que la onda adquirida por el DSA inicia varias muestras después que la onda adquirida por la otra tarjeta. ¿Es normal este comportamiento?

Solución:

Los dispositivos DSA utilizan un filtro digital con el propósito de remover componentes de frecuencia que se encuentren por encima de la frecuencia de Nyquist. Este filtro necesita una cantidad mínima de muestras para poder funcionar de forma efectiva, por lo que siempre habrá un retraso al iniciar las mediciones que por lo general, solo es evidente cuando se utiliza un disparo digital para iniciar la adquisición. Por favor revise las especificaciones del dispositivo que este utilizando para saber cual es el retraso exacto del filtro.

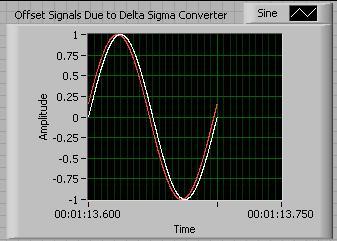

Por el efecto de este filtro, si las adquisiciones de un dispositivo DSA y otro que no lo sea inician al mismo tiempo, parecerá que la adquisición del dispositivo DSA inicia después que la del otro dispositivo, tal y como se muestra en la siguiente figura.

Por ejemplo, considere una tarea de lectura de datos iniciada por un disparo digital, en la cual se adquirirán 1000 muestras a una tasa de adquisición de 50 kS/s. Suponga que la señal es una señal TTL de 5 volts, la cual se conecta a un canal de entradas analógicas de un a tarjeta PXI-6255, y de una PXI-4461 (tarjeta de DSA), y que dicha señal también servirá como el disparo de la adquisición para ambos dispositivos. En la PXI-6255 el primer punto en el buffer de entrada del será el valor en alto de la señal TTL, ya que el buffer no contiene datos de antes de que se diera el disparo causado por el nivel alto de la señal. En cambio, la PXI-4461 cuenta con un retraso de 63 muestras cuando se utiliza a una tasa de 50 kS/s, por lo que la onda adquirida contará con 63 muestras en 0 V, las cuales se obtuvieron antes de recibir el disparo, y 937 muestras en 5 V. Cuando se grafiquen estas dos ondas en un mismo indicador, parecerá que la adquisición del DSA esta atrasada por 1.26 ms (63 muestras * 1/(50000 muestras/s)).

Este error se puede resolver en su mayoría, haciendo una lectura extra de los canales del dispositivo DSA, antes de leer simultáneamente con los dispositivos. En las siguientes lecturas, los datos deberían aparecer como alineados, ya que los datos que el dispositivo DSA adquirió antes del disparo deberían de haberse sacado del buffer de datos de entrada..

Algunos dispositivos DSA, como el PXIe-4464, soportan la propiedad AI.RemoveFilterDelay (DAQmx Channel Property Node: Analog Input»General Properties»Filter»Remove Filter Delay), la cual descarta de forma automática el atraso provocado por el filtro.

Ligas Relacionadas:

Manuales de Productos: NI Dynamic Signal Acquisition User Manual (noviembre 2010) (en inglés)

Productos y Servicios: Analizadores de Señales inámicas

Documento de Soporte 31LFSSWD: What is the Difference Between Analog and Digital Triggered Acquisition for the NI 447x Boards? (en inglés)

Documentos de Soporte 3EE7N2NQ: Synchronizing Dynamic Signal Acquisition (DSA) Products with NI-DAQmx (en inglés)

Documentos de Soporte 2WF8F22L: How Can I Synchronize NI PXI-4472 DSA Devices Across Multiple PXI Chassis? (en inglés)

Documentos de Soporte 4DAEUNNQ: How Can I Compensate for Different Group Delays with C Series Modules in LabVIEW FPGA? (en inglés)

Tutoriales: Synchronizing Analog Input C Series Modules with NI-DAQmx in LabVIEW (en inglés)

Archivos Adjuntos:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

Día del Reporte: 11/03/2016

Última Actualización: 05/29/2017

Identificación del Documento: 2UI8PGX4