我如何让LabVIEW忽略CLIP与LabVIEW FPGA模块框图之间的定时错误

主要软件: LabVIEW Modules>>LabVIEW FPGA Module

主要软件版本: 2014

主要软件修正版本: N/A

次要软件: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: 我的LabVIEW项目包括了一个CLIP,并且有多个输入输出信号连接到LabVIEW模块框图上,这些信号时在一个时钟域中赋的值,在另一个时钟域中读取,所以,他们之间的路径上的定时应该不匹配,然而,当我试图编译我的LabVIEW项目时,我收到了一个错误,提示在一个或者多个路径上出现了定时错误,我该如何让LabVIEW忽略这些路径上的定时错误

解答:

为了让LabVIEW忽略CLIP与LabVIEW FPGA模块框图之间的路径上的定时错误,你需要为该路径指定一个定时约束。该约束的类型以及语法取决于你的FPGA目标支持哪种编译工具,Xilinx ISE还是Xilinx Vivado

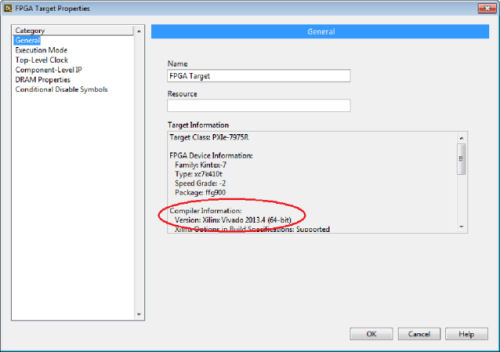

为了知道你的FPGA目标支持哪种编译工具,右键FPGA目标,选择Properties,在General选项卡中,在Target Information段,你可以看到一个字符串,列出了编译工具与版本,例如针对于Xilinx Vivado的Xilinx Vivado 201x.y或者针对Xilinx ISE的Xilinx 1x.y

Xilinx ISE使用分析

I如果你的CLIP组件在LabVIEW项目中目前不包含某个*.UCF约束,那么首先创建一个具有该扩展名的空文本文件

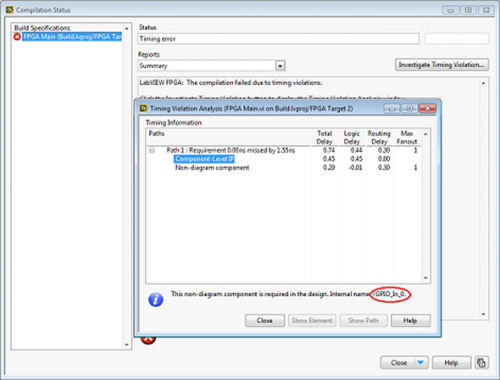

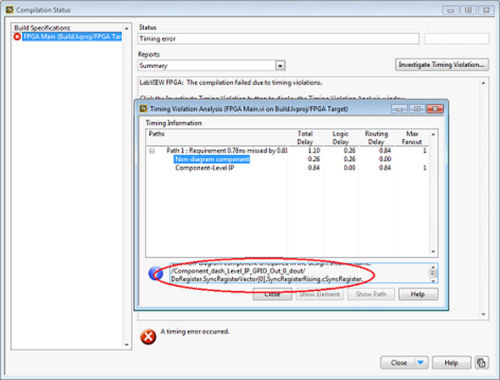

打开该*.UCF文件用于编辑,然后查看Compilation Status 窗口,找到失败的编译,点击Investigate Timing Violation…按钮,从而看到失败的路径的描述,查看源与目标路径注册的内部名称,如下方图中红色圈中所示,为了写入真实的约束,你将需要这两个名称

接着,在你的*.UCF文件中指定一个定时约束的from-to类型,这个定时约束应该包含一个足够大的值,从而保证编译工具能够完成,例如100ns,这个约束对于从CLIP流向LabVIEW FPGA模块框图的单比特信号有效,反之也有效,下方为示例语法:INST "*<internal name of the source register in the failing path>*" TNM = <source_path_name>; INST "*<internal name of the destination register in the failing path>*" TNM = <destination_path_name>; TIMESPEC "<constraint_name>"= FROM "<source_path_name>" TO "<destination_path_name>" 100 ns DATAPATHONLY;

在上方的约束中,<internal name of the source register in the failing path> 指的是源source register的内部名称,查看上方第一个图中的画圈的 /GPIO_ In_0,正如 Timing Violation Analysis 窗口所示

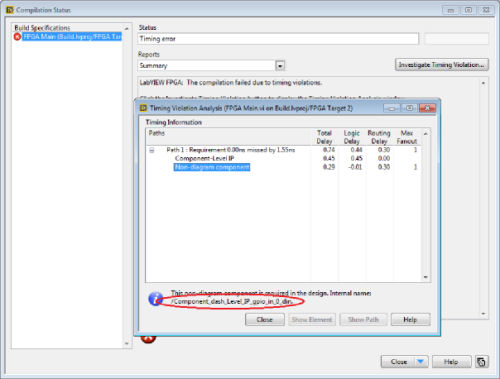

在上方的约束中,<internal name of the destination register in the failing path>指的是 destination register的内部名称,查看上方第二个图中的画圈的/Component_dash_Level_IP_gpio_in_0_din ,正如Timing Violation Analysis 窗口所示

在上方的约束中,<source_path_name>以及<destination_path_name>是你在*.UCF文件中赋予source register与destination register的唯一的名称,这些名称必须以TNM开头,后面紧跟着的是任何字母数字或者下划线。

在上方的约束中,<constraint_name>是赋予*.UCF文件中FROM-TO约束本身的名称,这个名称必须以TS开头,后面跟着字母数字或者下划线

下面,将上方的约束加到*.UCF文件中,并在相关领域想加入关键信息

下方是一个完整的Xilinx ISE约束的例子,基于的是上方的Timing Violation Analysis分析窗口INST "*/Component_dash_Level_IP_gpio_out_0_dout*" TNM = TNM_C1; INST "*/Component_dash_Level_IP_gpio_in_0_din*" TNM = TNM_C2; TIMESPEC "TS_Clip1"= FROM "TNM_C1" TO "TNM_C2" 100 ns DATAPATHONLY;

编辑完*.UCF文件后,保存并且关闭,然后,编辑CLIP声明,如果你为了解决定时错误而创建了这些文件的话,将*.UCF文件添加进去

Xilinx Vivado使用情况

如果你的CLIP组件目前在LabVIEW项目中没有包括.*XDC约束文件,首先创建一个后缀为*.XDC的约束

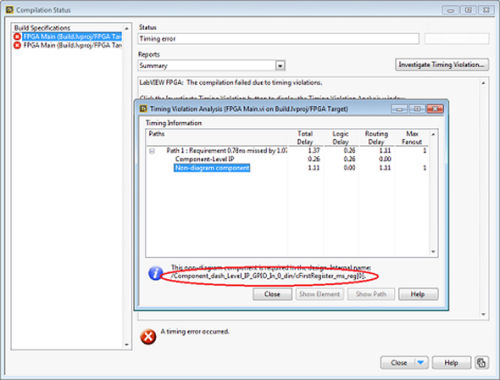

打开该文件用于编辑,然后查看Compilation Status 窗口,找到失败的编译,然后点击Investigate Timing Violation…按钮,从而查看失败路径的描述,查看源与目的的内部名称,查看下方两张图中的红色圈区域,你将会在填写真正的约束时用到这些信息

该约束要求在失败的路径上忽略定时,它的语法依据该路径是从CLIP到LabVIEW FPGA模块框图的输入路径还是反过来的输出路径而不同

数字输入情况

在Xilinx Vivado数字输入情况中,约束将忽略具有一个特定目的的失败路径上的定时,可以从Timing Violation Analysis 窗口提取,下面是一个语法的示例:set_false_path -to [get_cells *<internal name of the destination register in the failing path>]

在上方的约束中,<internal name of the destination register in the failing path> 指的是destination register的内部名称,查看Timing Violation Analysis 窗口中画圈的代码/Component_dash_Level_IP_GPIO_In_0_din/cFirstRegister_ms_reg[0]

将上方的约束添加到*.XDC文件中,并将将相关信息填入必要的区域中

下面是一个完整的约束的例子,基于的是上方图中的Timing Violation Analysis 窗口:set_false_path -to [get_cells */Component_dash_Level_IP_GPIO_In_0_din/cFirstRegister_ms_reg[0]]

数字输出情况

在Xilinx Vivado数字输出情况中,约束将会把具有特定源的失败路径上的定时忽略,该信息从Timing Violation Analysis 窗口中提取。下面是一个示例语法:set_false_path -from [get_cells *<internal name of the source register in the failing path>]

在上方的约束中,<internal name of the source register in the failing path>指的是 source register的内部名称,参考下图中Timing Violation Analysis 窗口的画圈区域的代码 /Component_dash_Level_IP_GPIO_Out_0_dout/DoRegister.SyncRegisterVector[0].SyncRegisterRising.cSyncRegister

将上方的约束添加到*.XDC文件中,并且将相关信息填入必要的区域

下方是一个完整的约束的例子,基于的是上方图中的 Timing Violation Analysis 窗口set_false_path -from [get_cells */Component_dash_Level_IP_GPIO_Out_0_dout/DoRegister.SyncRegisterVector[0].SyncRegisterRising.cSyncRegister]

编辑好*.XDC文件后,保存并且关闭,然后,编辑该CLIP声明,如果为了修改这些定时错误而创建了这个文件的话,将该*.XDC文件添加进去

最后,重新新建LabVIEW项目,该路径上的定时错误就会消失了

相关链接:

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 08/12/2014

最近更新: 02/27/2015

文档编号: 6OB8E8FM