Memory Read 노드를 SCTL에 위치시키면 Code Generation Errors를 반출합니다.

주요한 소프트웨어:

주요한 소프트웨어 버전: 1.0

문제가 해결된 소프트웨어 버전: N/A

부차적인 소프트웨어: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

문제점: LabVIEW FPGA VI에서, Memory Read 노드를 Single-Cycle Timed Loop (SCTL)안에 위치시킨 상태로 컴파일을 수행하면 다음과 같은 에러가 발생합니다:

Internally pipelined object(s) not connected to a feedback node

왜 이런 문제가 발생하며고 어떻게 해결할 수 있습니까?

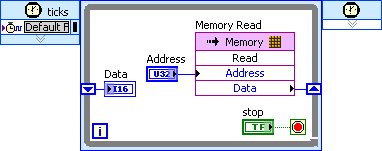

솔루션: 이 에러가 발생하는 이유는 Memory Read 메소드는 실행하는데 1 클럭 사이클이 필요하기 때문입니다.(LabVIEW FPGA Module Help: Read (Memory Method) Details). 만약 SCTL안에 사용을 해야 한다면 코드를 Pipeline 으로 만드는 것이 필요합니다. 이는 1 클럭 사이클 동안 데이터를 읽고, 데이터 인디케이터가 다음 사이클에서 업데이트 될 수 있도록 합니다. 결과적으로, 1 사이클의 지연이 생깁니다. Figure 1을 보시면 Pipeline된 코드를 확인하실 수 있습니다.

Figure 1. Memory Node in SCTL.

Pipeline 된 코드를 사용하려면, Memory 노드의 출력 부분을 SCTL의 가장자리에 붙이고 우클릭하여 "시프트 레지스터로 대체"라는 항목을 선택해야 합니다. 그리고 시프트 레지스터의 왼쪽 부분에 생성되는 부분에 우클릭을 하고 생성>>인디케이터를 눌러 인디케이터를 생성해 주어야 합니다.

Note: Feedback node 를 시프트 레지스터 대신 사용하여 같은 기능을 구현할 수 있습니다.

Note: Pipelining을 이용하여 코드에 지연을 추가할 때, Handshaking 터미널을 고려하여 코드가 어떻게 다른 부분과 상호 작용할 수 있는지 생각해야 합니다.

Note: 분주된 타이밍 소스로 SCTL를 천천히 돌게 하는 것으로는 이 에러를 해결할 수 없습니다.

관련 링크:

LabVIEW 2013 FPGA Module Help: Pipelining to Optimize FPGA VIs (FPGA Module)

LabVIEW 2013 FPGA Module Help: Read (Memory Method)

LabVIEW 2013 FPGA Module Help: Sheduling Timing Using Handshaking Signals (FPGA Module)

LabVIEW 2013 FPGA Module Help: Storing Data between Loop Iterations (FPGA Module)

첨부:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

리포트 날짜: 03/21/2009

마지막 업데이트: 02/04/2015

문서 번호: 4VKJ23DK