当使用NI的FlexRIO时,出现“由于Xilinx错误编译失败”的错误

硬件: Modular Instruments>>FlexRIO>>PXI-7951R, Modular Instruments>>FlexRIO>>PXI-7954R, Modular Instruments>>FlexRIO>>PXI-7952R, Modular Instruments>>FlexRIO>>PXI-7953R, Modular Instruments>>FlexRIO>>PXIe-7962R, Modular Instruments>>FlexRIO>>PXIe-7961R, Modular Instruments>>FlexRIO>>PXIe-7965R

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

只是一个关于用LabVIEW FPGA 2010 不能编译NI FlexRIO FPGA VIs的问题,要解决这个问题,你必须安装软件补丁到程序库中。

当满足以下条件时, LabVIEW FPGA VI可能会编译失败:

- 使用LabVIEW FPGA 2010编译 ;

- 把一个PXIe NI FlexRIO FPGA 模块NI PXIe-7961R, NI PXIe-7962R, 或者 NI PXIe-7965R作为目标;

- 使用以下的NI FlexRIO适配器或者CLIP条目NI 5751, NI 5752, NI 5761, NI 5762, NI 5781 系统同步CLIP, NI 6587。

解答:

这个问题是由使用 LabVIEW FPGA 2010中XIlinx ISE编译器的一个漏洞引起的。当这个问题出现,用来通过适配器模块CLIP条目放置IODelayCtrl组件的请求可能会失败。

出现错误“由于资源重复导致编译失败” 当您使用NI FlexRIO时,除了使用以下的步骤解决这个问题,NI推荐您采用知识库里列出的步骤。

- 关闭LabvVIEW和运行在您电脑上的任何编译工作。下载附加文件<patch.zip>。

- 取出这个文件的内容并且复制程序目录到磁盘上的NIFGPA文件目录下。这个目录位于:C:\NIFPGA for Windows XP and Windows 7。

- 点击是,取代任何冲突的文件。这将取代XIlinx ISE安装目录下受影响的文件。

- 右键单击我的电脑,选择属性 。

- 对于Window7系统,点击高级系统设定。

- 设置高级选项卡。

- 点击环境变量。

- 在系统变量类别中,点击New创建一个新的环境变量。

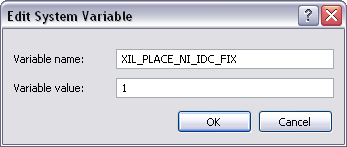

- 输入XIL_PLACE_NI_IDC_FIX作为环境变量名 。

- 输入变量值1,使用下面的图片作为参考。

- 点击OK创建环境变量,点击OK退出环境变量窗口,点击OK退出系统属性窗口。

- 重启电脑让变量生效。

以供参考,这个问题可能引起以下的问题的一种

错误例子1:

在一些情况下,XIlinx ISE编译器在编译的映射阶段可能崩溃。在这种情况下,Windows或者Visual Studio 实时调试,返回一个错误表明映射的应用程序进程已经失败。

LabVIEW也会返回类似下面的错误:

由于Xilinx错误导致编译失败。

详细:

错误:TclTasksC:process_077: 未完成. 当执行程序运行“Generate Post-Map Static Timing”,请检查.false的记录和报告文件。

(file "C:\NIFPGA\jobs\entb5e7_V5WxwWH\mapTrce.tcl" line 8)

错误: 映射NCD文件"Puma20Top_map.ncd"没有找到.

请首先运行“映射报告”进程生成映射NCD文件。或者在“Pre-Route Static Timing Report”进程右击鼠标选择全部运行。

错误例子2:

Xilinx ISE编译器能报告在设计中需求的IODelayCtrl组件没有找到。在这种情况下,一个下面类似的错误在LabVIEW编译概述窗口出现:

由于Xilinx错误导致编译失败。

详细:

错误:TclTasksC:process_077: 未完成. 当执行程序运行“Map”,请检查.false的记录和报告文件。 (file "C:\NIFPGA\jobs\MP5f213_KI40c7b\map.tcl" line 8)

错误:PhysDesignRules:1613 - 对于时钟区域CLOCKREGION_X0Y4不能找到IDELAYCTRL The IODELAY block

Puma20Window/theCLIPs/IO_Module_CLIP0/Ni5761Topx/Ni5761AdcSamplerx/

Ni5761CaptureAdcx/Data01Capture/GenMasterMonitor[3].

主Idelay有一个固定量或者变量的Idelay类型,这个程序要求在同样的时钟区域有一个程序化的IDELAYCTRL块

如果您在安装补丁时遇到任何问题,请联系国家仪器

相关链接: Knowledgebase 5E4FNCDP: Error, “Compilation Failed Due to Resource Overmapping,” When Using NI FlexRIO

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 12/16/2010

最近更新: 06/26/2011

文档编号: 5GFAB7DP