Labview FPGA Timing VIs的时钟源是什么?

主要软件:

主要软件版本: 2011

主要软件修正版本: N/A

次要软件: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: Labview FPGA Timing VIs的时钟源是什么,时间计数的输出可以被交换使用么?

解答:

所有的FPGA时序函数都是基于RIO硬件中相同的内部计数设备。但是它们在时间计数时并不拥有相同的开始时间。在FPGA芯片的有限尺寸中,你必须一直关注资源的使用,并将其尽可能的降低。当在相同的VI中使用多个时序函数时,理解它们如何协同工作,哪一些可以被同时使用哪一些不可以就显得十分重要。

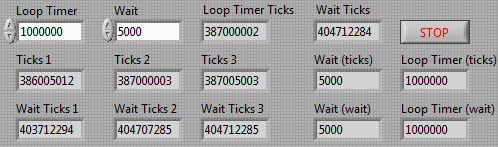

1. 使用滴答计数输出

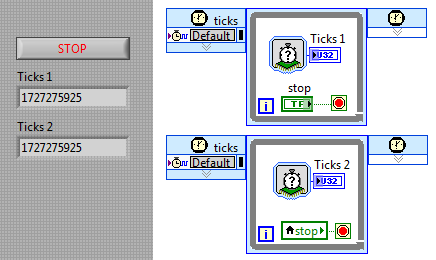

当标定FPGA代码的执行时间时,时间计数VI非常有效。但你可能注意到,其他两个时序函数同样有时间计数的输出,怀疑它们之间是否兼容。时间计数和等待下一个整数倍时间函数使用相同的开始时间,而等待函数输出滴答计数时使用不同的开始时间。如下面的VI所示,

因为这些差异,一起使用等待VI和时间计数VI并不能稳定可靠的测试代码。如果你计划使用一个等待函数,你需要使用所有的等待VI,并给它们一个0输入。这和时间计数VI的功能几乎如出一辙,当然,这需要保证其他的等待VI实例使用一个匹配的时钟。

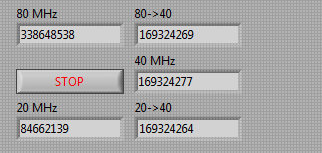

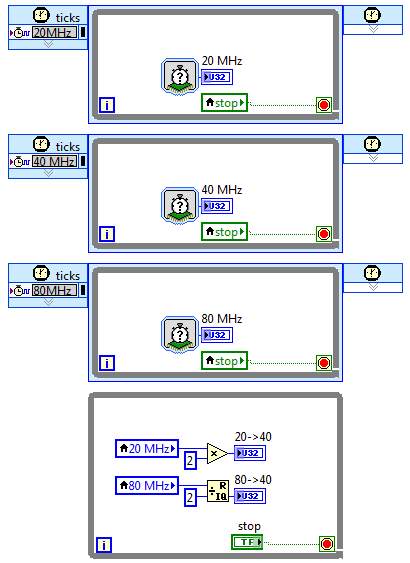

2. 在不同的循环中使用时间计数VI.

你也可以在单周期定时循环中使用滴答计数VI,但这将导致它们在在那一个循环中使用这个频率进行计数。它们将保持相同的开始时间,你可以改变这些数值以使得它们兼容但并不完全相同。因为单周期定时,比例函数不能总在循环的内部执行。在另一个循环中执行的话会因为值的微小偏离导致竞争情况的出现。如下面的VI所示:

但是如果这些循环在相同的频率中运行,那么滴时间计数将会保持同步。

需要关于时序函数方面的更多信息,请察看FPGA Module Timing VIs help document. 下面也有关于单周期定时循环和竞争方面的链接。

相关链接: LabVIEW 2011 Help: Timing VIs (FPGA Module)

KnowledgeBase 42OGRRTQ: Single-Cycle Timed Loop FAQ for the LabVIEW FPGA Module

KnowledgeBase 3RCIP96K: How Do I Implement a Custom Single Cycle Timed Loop Rate in LabVIEW FPGA?

KnowledgeBase 28Q6L7B5: Using a Local, Global, or Shared Variable in Parallel Loops Can Cause Race Conditions

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 09/23/2011

最近更新: 11/28/2011

文档编号: 5PMAG6ES