HSDIO NI 655x系列进行采集时可能导致错误的原因

硬件: Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6551, Digital I/O (DIO)>>High-Speed Digital I/O>>PXI-6552, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6551, Digital I/O (DIO)>>High-Speed Digital I/O>>PCI-6552

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: 我在用NI 6551和NI 6552两个设备进行数字波形采集,我采集到的数据并不是我认为我应该采集到的。此外,我用示波器或者数字万用表在线检测,我发现逻辑电平并不是我希望得到的,为什么会导致这个现象?

解答:

三个原因可能造成这些问题。以下这些可能的原因都能够通过配置您的NI 655x来修复:

- 输入阻抗不匹配

- 采集的同时也在驱动该通道

- 可编程逻辑电平

输入阻抗不匹配

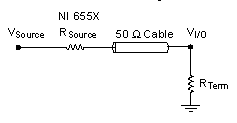

NI 655x可以配置为50欧或者50K欧的输入阻抗。50欧的输入阻抗是为了用来对一些需要阻止信号反射的系统做阻抗匹配。这个设置会导致电压的分压;测量得到的逻辑幅度将会变为源信号电平的一半。在一些反射可以被接受的应用中,可以选择50K欧的输入阻抗。图1显示了50欧输入阻抗在50欧源阻抗下电压分压效果。

图1 NI 655x输入阻抗

采集的同时也在驱动

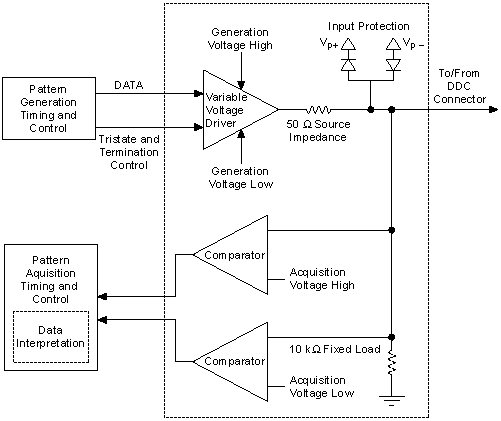

NI 655x系列在生成波形的同时也可以采集。这个能力可以让您采集你刚生成的波形,或者你可以在另一设备正在驱动该线路的同时生成波形。为了防止其他设备驱动该线路,这时候你可以将该通道配置为三态。该操作能有效的将驱动电路从该线路中移除。NI 655x的通道的电路图可以在图2中可出。注意生成模式的电路与采集模式的电路是分离并且独立的。

图2 NI 655x通道电路示意图

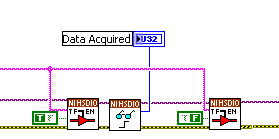

为了将通道设置为三态,利用niHSDIO Tristate Channel这个VI。该VI有个布尔输入,设置为“真”即使能三态,设置为“假”则禁止三态。该VI正确使用方法如图3。该图中在 niHSDIO Read Static (U32) VI 被调用的时候,三态被使能。

图3 先使能后禁止三态

可编程逻辑电平

NI 655x允许您编程分别的设置逻辑真与逻辑假的高低电压水平。这个灵活的设置需要您知道信号到来NI 655x通道时的幅度。如果高低电压值没有设置正确,该板卡则不会正确识别到电平的逻辑值,也就是说你会丢失数据。

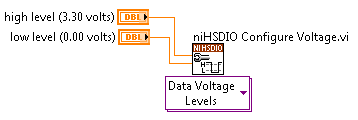

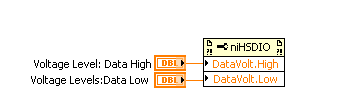

电压水平可以以10mV的增量在-2V与+5.5V之间设置。 如图4,niHSDIO Configure Voltage.vi 与niHSDIO属性节点可以用来设置电压输入的高低电压水平。

图4 NI 655x的高低输入电平

相关链接: KnowledgeBase 42JET3JQ: Per Cycle Tristate Programming with NI-HSDIO

Developer Zone Tutorial: Testing Protection/Clamp Diodes with the NI 655x Digital Waveform Generator/Analyzer

KnowledgeBase 3TICD8VB: How Do I Change the Input Impedance of my NI 655x?

Products and Services: NI 655x Digital Waveform Generator/Analyzer

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 10/23/2007

最近更新: 09/06/2012

文档编号: 4EMLPRVZ