在LabVIEW FPGA 中使用VHDL 代码

主要软件:

主要软件版本: 8.0

主要软件修正版本: N/A

次要软件: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

我已经有了执行一定操作的VHDL代码,我并不想重建基于LabVIEW FPGA的代码。那么如何才能在LabVIEW中使用VHDL代码呢?

解答:

如果您已经有了LabVIEW 8.6.x或更新版本,您可以使用CLIP节点来导入您的VHDL代码。这个LabVIEW的新特性提供了将您的IP整合至LabVIEW FPGA中的另一种方法。想学习如何使用CLIP节点以及它和HDL节点的差别,请查看教程Developer Zone Tutorial: Importing External IP into LabVIEW FPGA with the CLIP Node或者根据以下相关链接查看随选培训模块。

另一个选择是创建一个HDL 节点。以下的简单的例子演示了如何使用HDL节点将已有的VHDL代码与LabVIEW FPGA整合在一起。参考以下步骤来使用VHDL代码,该代码实现了FPGA中两个32位整型数相加。

步骤:

1. 创建一个包含FPGA目标(R系列或CompactRIO)的项目。请参考LabVIEW帮助以获得更多如何将FPGA目标包含至项目的信息。

2.在FPGA目标中创建一个VI。请右击项目中的FPGA目标并选择新建>>VI。在编程>>高级>>HDL Node中找到HDL Interface Node,并放置于程序面板中,如下图:

3.双击HDL Interface node。在弹出的对话框中输入参数(如下图)。下图中,’x’和’y’是两个待相加的32位整型数。’result’是’x’和’y’的加和值。

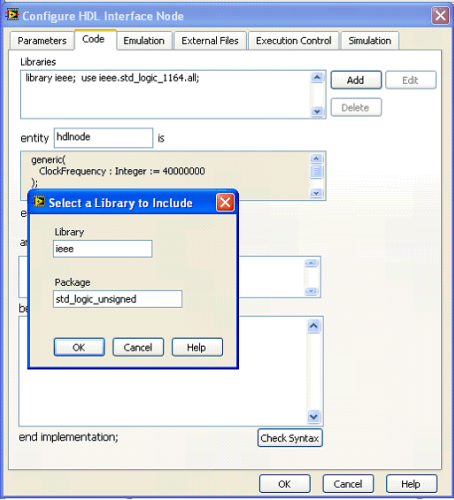

4.选择Code选项卡。点击“Add”按钮并且按下图所示在“Select a library to include”对话框中填入。点击“OK”。

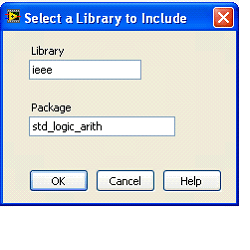

5. 重复步骤4,并按下图包含相应的库。

以上的库是必须被包含的,因为FPGA认为32整型数是一个由32个二进制数组成的数组。因为是对两个数字的加和,以上被包含的库就是为了使能数学的“+”操作的重载。通过运算符的重载,这意味着一个操作符能操作比当初更多的数据类型。举个例子,对数组的价格并不是一个定义的操作,然而,在包含了以上的库之后,这就使能了二进制数组的加和。

6. 在“begin”的部分,输入以下代码:

process( clk, reset )

begin

if( reset = '1' ) then

result <= (others=>'0');

elsif rising_edge(clk) then

if enable_in = '1' then -- use enable_in as a clock enable

result <= x + y; -- result follows the inputs by one clock cycle

end if;

end if;

end process;

enable_out <= enable_in; -- drive the enable_out with enable_in

这是进行加和运算的VHDL代码

7. 点击Check Syntax 按钮。在成功编译后,点击OK。

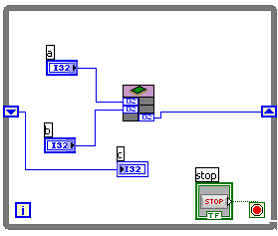

8. 按下图完成LabVIEW后面板上的代码:

9. 点击该VI的运行按钮。这将编译并在FPGADeveloper Zone Tutorial: Importing HDL Code into FPGA VIs Using the HDL Interface Node

Developer Zone Tutorial: Importing External IP into LabVIEW FPGA with the CLIP Node

On-Demand Training: Importing External Codes into LabVIEW FPGA Using CLIP (SSP Required)

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 03/16/2006

最近更新: 11/30/2010

文档编号: 3VFES8FZ