我如何在程式中重置〈Reset〉我的 CompactRIO 控制器

主要軟體:

主要軟體版本: 1.1

主要軟體修正版本: N/A

次要軟體: N/A

硬體: CompactRIO, CompactRIO, Reconfigurable I/O (RIO)

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

問題: 我想要在程式中重置我的 CompactRIO 控制器。這是可行的嗎?

解答:

有兩個方法可以用程式重置 CompactRIO 控制器,一個是使用 RT Reboot Controller VI 。關於這個 VI 的使用請參考這篇文章: "Can a LabVIEW Real-Time Controller Reboot Itself?" 另一個方法則是使用 FPGA 。 CompactRIO 上有系統重置的數位信號線 (Digital line) ,當設為true時會重置系統。以下介紹如何使用此系統重置線。

LabVIEW 8.5 及以後的版本

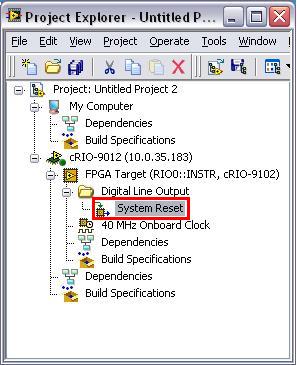

在 LabVIEW project 加入 CompactRIO controller 以及 FPGA 背板時,系統重置線會自動加入Project。您只要直接拖曳系統重置線到您 FPGA VI 的 Block diagram 來建立此 I/O ,並連接 True 常數到其輸入端,就可以重置 CompactRIO controller 。系統重置線在 LabVIEW 8.5 及以後版本 Project中的位置請參考下圖。

LabVIEW 8.2 和 8.0

在 LabVIEW 8.x 中加入這個數位 I/O,請完成以下步驟

1. 在 Project Explorer 視窗中對著 FPGA target 按右鍵選擇 New»FPGA I/O

2. 將 Digital Line Output 這個部分展開,選擇 System Reset,並按下 Add 按鈕

3. 一旦將這個 I/O node 加入 project,您就可以將它拖曳到您 FPGA VI 的程式區,並且將一個 boolean true 送到這個 I/O 來重置 CompactRIO 控制器。

下圖說明了加入了 System Reset I/O 的 LabVIEW 8.2 或 8.0 project 。

LabVIEW 7.1

在 LabVIEW 7.1 中加入這個數位 I/O,請完成以下步驟

1. 在 LabVIEW target 中選擇 FPGA 裝置並開啟您的 FPGA project。

2. 在程式區中放上一個 Digital Output I/O Node

3. 雙擊這個 I/O node 來開啟 Configure Digital Output 對話框

4. 在這個對話框的 General tab 分頁中,從下拉式選單中選擇 System Reset 這個接點〈terminal〉,接著關閉 Configure Digital Output 對話框。

5. 將一個 boolean True 常數輸入這個 I/O node,那麼當程式執行到這個 I/O node 時就會重置 CompactRIO 控制器。

下圖中展示了Configure Digital Output 對話框。

相關連結: KnowledgeBase 381EBOQS: Can a LabVIEW Real-Time Controller Reboot Itself?

KnowledgeBase 4L6A2R69: Why Does the cRIO Hang when Resetting the Controller with System Reset?

附加檔案:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

報告日期: 10/17/2005

最後更新: 12/28/2012

文件偏號: 3QG99N8T