同步PXI-6682H上的10MHz晶振和秒脉冲信号

主要软件:

主要软件版本: 2010 SP1

主要软件修正版本: N/A

次要软件: Driver Software>>NI-Sync

硬件: PXI/CompactPCI>>Platform Modules>>Timing and Synchronization>>PXI-6682, PXI/CompactPCI>>Platform Modules>>Timing and Synchronization>>PXIe-6674T

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: 我很熟悉定时和同步,并且建立了应用程序使PXI-6682上的10MHz的TCXO板载晶振同步到秒脉冲信号。但当我把这个信号路由出去,并且通过示波器或LabVIEW中进行测量时,发现他们有时会发生漂移并且不再同步。哪里出错了?

解答:

由于直接数字合成(DDS)是通过PXI-6682的板载FPGA中的计时器实现的,秒脉冲信号就不会与10MHz的晶振信号绝对的对齐。这是因为PXIe的背板100MHz的时基是通过DDS技术从212.5MHz的晶振中派生出来的,而这时基正是驱动6682上的FPGA的。

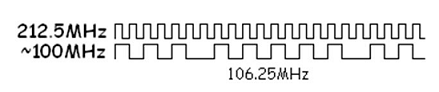

这就产生了平均100MHz的信号中夹杂着个别106.25MHz的脉冲信号。这些不均匀的106.25MHz的信号表现的像100MHz的信号一样在与FPGA的计时器连接时会出现偶尔的跳沿现象。具体可参考下图。

这是PXI-6682上板载TCXO晶振的而一个硬件上的限制,但可以通过用NI PXI-6653或者NI PXI-6674T的时钟约束来修正。在这些设备上,使用的是更加稳定的OCXO而不是TCXO来控制DDS,这样避免了偶尔的跳沿。

按照上面的操作,一个不稳定的100MHz的时钟会变成稳定的100MHz时钟,这样就有唯一的沿变化率。在这种情形下,秒脉冲信号和10MHz的晶振信号的对齐会随时间的变化保持一个稳定的相位关系。

相关链接: Multi-device PXI_Clk10 Disciplining 1.1 - Windows 7/XP x86/Vista, Real-Time OS

Synchronization Frequency for PXI-6682 and PCI-1588 Implementing PTP

Understanding Direct Digital Synthesis (DDS)

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 06/13/2011

最近更新: 11/28/2011

文档编号: 5MCA7HJ3