是否有可能讓我在R-Series板子上的FPGA上把數位訊號設定為Tri-State的模式?

主要軟體:

主要軟體版本:

主要軟體修正版本:

次要軟體: LabVIEW Modules>>LabVIEW FPGA Module

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

問題: 我想要把我R-Series板子上的DIO訊號設定為Tri-State模式並且把它放在Single Cycle Timed Loop(SCTL)裡. 這樣做有可能嗎?

解答:

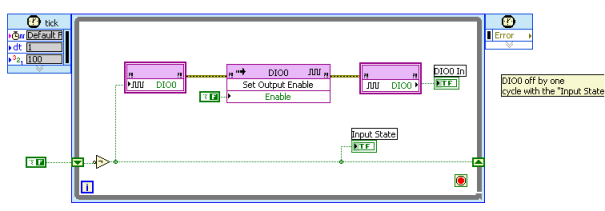

R-Series板子上的數位訊號都是雙向的, 這表示它可以被視為可Tri-State的數位訊號. 當您加入了一個 FPGA I/O Method Node 並把 Set Output Enable 設為 True 時, 這個DIO訊號就會被設為輸出. 當您把這個設定設為 False (high impedence) 時, 此DIO訊號就會被定義為輸入. 當您想要輸入的訊號時, 您必須把 Set Output Enable 設為 False, 不然您讀進來的資料就會是您寫出去的資料. 由於此設定 (Set Output Enable) 可以放在一個 Single Cycle Timed Loop內, 這樣可以允許Tri-State在一個Cycle內被完成. 但是, 在底層執行此方式時, DIO讀取, Set Output Enable 跟 DIO設定 (如下圖) 都各需要一個Cycle來完成. 所以實際上當我們把這些設定放入一個SCTL時, 就會執行一個內部的Pipe Line方式. 實際的訊號可能就因此會超出一個或大於一個Cycle.

以下是一個實際Benchmark此方式的貼圖. 當"DIO In" 與 "Input State" 比較完時, "DIO In" 就已晚了一個Cycle.

相關連結:

附加檔案:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

報告日期: 10/24/2008

最後更新: 04/30/2009

文件偏號: 4QNHGPL1