创建一个延时可重触发的有限脉冲序列发生器

主要软件:

主要软件版本: 8.5

主要软件修正版本: N/A

次要软件: N/A

硬件: Multifunction DAQ (MIO)>>E Series

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

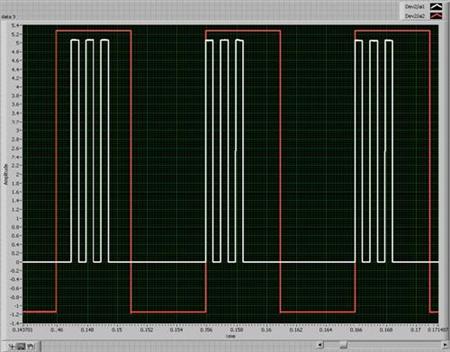

我想要创建一个延时的可重触发的有限脉冲序列。当脉冲序列中只有一个脉冲时,可以达到预期的效果(图1所示)。但当我尝试产生一个延时的可重触发的有限脉冲序列时,延时只在第一次触发时正确显示,但之后的就不是这样了(图2所示)。对于之后的触发,计数器立即动作且即使在设置过低时间的情况下,有限脉冲序列还是会被无延时地触发。我应该如何改正这个?

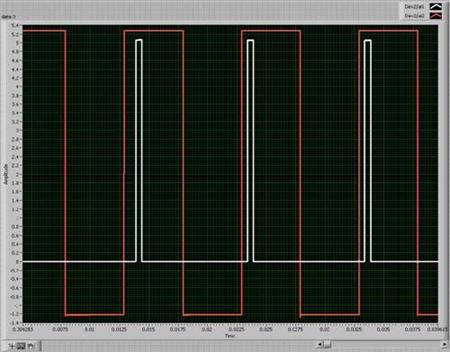

图1. 延时可重触发单脉冲(1kHz脉冲序列 + 1ms初始延时)

图2. 延时可重触发脉冲序列(1kHz脉冲序列 + 1ms初始延时)

解答:

具有STC3时序引擎的设备:

如果你正在使用基于STC3的设备,你可以使用一个新的属性节点来使能可重触发序列的初始延时。这个属性可以在DAQmx通道 » 计数器输出 » 常规属性 »更多 » 启用触发器的初始延时。

较老的设备:

为了产生一个多个脉冲的延时可重触发的有限脉冲序列,在芯片配置较老设备上必须使用两个计数器。

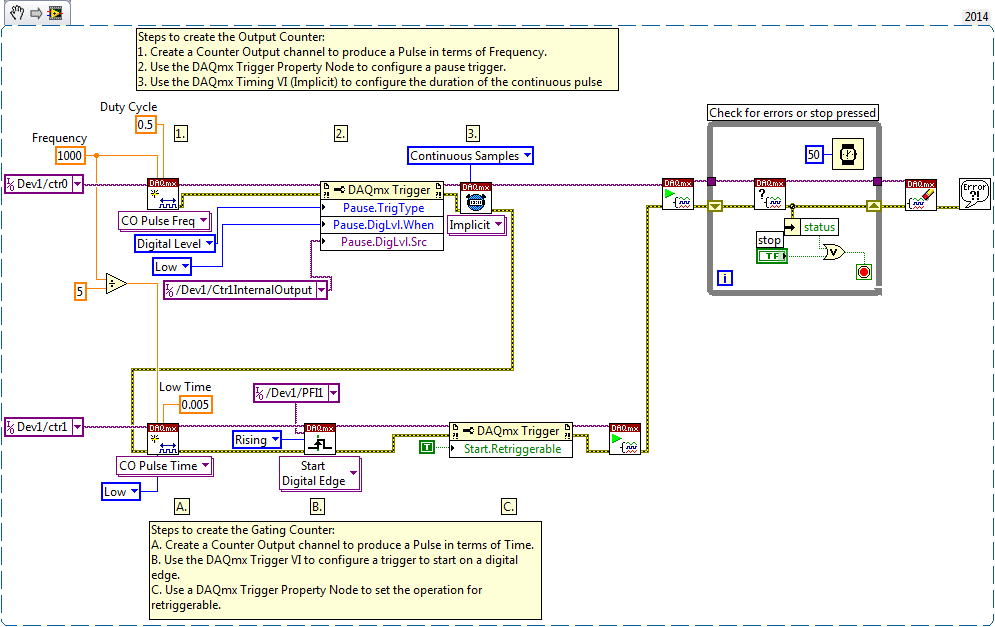

第一个计数器(ctr0)需要配置在OUT端输出一个连续的脉冲序列。这个脉冲序列连接到第二个计数器(ctr1)的门端。使用DAQmx触发属性节点,可以将连续脉冲序列配置成在第二个计数器内部输出为低时暂停。这意味着只有当ctr1为高时脉冲才可见,所以连续脉冲序列被配置成了有限脉冲序列。

图3对一个LabVIEW VI进行了阐述(后面有链接)。可见脉冲的数量可以通过将连续脉冲序列的频率(1000HZ)除以想要的脉冲数(5)进行配置。这给了门控计数器5ms的高时间。低时间也同时被配置成5ms。这就意味着当接收到触发时,在这个例子中是PFI 1口,在5个脉冲出现之前会有5ms的低时间。这有效地在每个可重触发发生器之前创建了一个延时。

图3. LabVIEW 范例程序

相关链接:

KnowledgeBase 2P5EJFUV: How Can I Set the Counters on My E Series DAQ Card to Achieve a Re-Triggerable Analog Input Acquisition?

KnowledgeBase 3ZPA11IU: Using One Counter to Generate a Retriggerable Finite Digital Pulse Train with a PCI-6602 and DAQmx

KnowledgeBase 2JDFL3XA: Finite Pulse Train Generation Triggered by Both Rising and Falling Edges of a Trigger Pulse Using Analog Triggering

KnowledgeBase 1VQ9J3LL: Configuring an Analog Input Acquisition with Multiple Triggers on an E Series DAQ Device

KnowledgeBase 3GSKKKR6: Different Counter Retrigger and Initial Delay Behavior in Traditional (Legacy) NI-DAQ and NI-DAQmx

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 10/17/2007

最近更新: 07/21/2016

文档编号: 4EG9AN46