如何生成以及集成Aurora IP到LabVIEW工程中

主要软件: LabVIEW Modules>>LabVIEW FPGA Module

主要软件版本: 2014

主要软件修正版本: N/A

次要软件: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题: 我正在使用高速串行设备板卡NI 6591R或是6592R,我尝试生成Xilinx的Aurora IP核并将其使用在我的应用中。那么我需要知道哪些步骤才能顺利生成这个IP核并将其集成在我的应用中呢?

解答:

如何生成以及集成Aurora IP到LabVIEW工程中

我正在使用高速串行设备板卡NI 6591R或是6592R,我尝试生成Xilinx的Aurora IP核并将其使用在我的应用中。那么我需要知道哪些步骤才能顺利生成这个IP核并将其集成在我的应用中呢?

关于如何生成和集成一个特定的IP核(Aurora)到LabVIEW工程中,这里有详细步骤(以及解释),在集成后您就可以使用那个IP核进行编译和使用了。

1. 准备工作

为您的设备安装合适的软件和驱动。请参考本文相关链接段中板卡的起步向导文档。

参考第6节中:为NI 6591R/6592R开发应用程序,需要知道更详细信息,请根据以下步骤进行:

2. 打开Vivado

提示:Vivado 2013.4仅支持Windows7.

到以下路径打开Xilinx的Vivado工具:

C:\NIFPGA\programs\VivadoXXXX_Y\bin\vivado.bat

其中XXXX_Y是需要打开的Vivado版本。

3. 创建一个IP工程

在这一步骤中您需要创建一个新的工程,并需要根据向导来完成整个流程。6591R使用的FPGA型号为xc7k410tffg900-3,而6592R使用的FPGA型号为xc7k410tffg900-2,这个在创建新项目的时候需要您进行选择。

在新项目创建完毕以后,你需要按照Vivado中的IP目录的步骤来添加IP核。

4. 从IP目录中选择Aurora IP核

在这一步中选择您需要的编码方式。我们将会使用64b/66b的IP核。双击IP核打开用户定义编辑窗口。这时候可能会要求您生成输出产品,如果是这样,就点击生成。

5. 修改核的属性

用户手册中,NI推荐不要对DRP使用AXI4-Lite,所以在这一步里面选择“本地”。针对这个例子,所有其他的核的选择都保持为原来的默认值。

在GT选择页中,我们将继续在Quad 3上实现一个端口。根据6591R/92R上端口的位置信息,我们将做以下的选择:

完成这一步设置后,点击OK并生成IP核产品。您将得到以下一个综合后的IP核文件(.Xci文件)。

提示: 范例的工程自带的一个用于CLIP范例程序的.xci文件包括所有的核配置。

下图中是IP标签页显示:

6. 创建.edf网表文件

如果你使用的IP核是用Verilog来编写的,那么就必须要有一个网表文件才能成功地进行编译。在源窗口中右击.xci文件,并选择打开IP核范例设计…

在Vivado新弹出的窗口中,选择一个你希望创建网表文件的顶层文件,点击左边的运行综合。

在综合完成后,通过以下一种方式选择并打开综合后的设计:

1. 在弹出窗口中。

2. 选择左侧窗口中综合下的打开综合后的项目选项。

3. 打开运行设计标签,右击,选择打开综合后的设计。

需要选择打开综合后设计的弹出窗口如下所示:

使用如下的Tcl命令来写.edf文件:

write_edif <name of entity>.edf

这个命令行将会生成一个网表文件,后期您需要通过它来导入IP核到您的LabVIEW工程中。您可以在Tcl的调试窗口信息中找到文件的路径。

对于这个Aurora范例程序来说,几个.edf文件都是通过这个方法来创建,包括:

要为这几个特定的模块建立.edf文件,需要继续在Vivado的综合设计窗口中,在网表窗口中您也可以看到与该设计相关的几个单元。

输入以下命令行,来创建相关单元的.edf文件:

write_edif -cell <name of cell> <file name>.edf

例如,要创建clock_module.edf的话,命令就是:

write_edif -cell clock_module_i aurora_64b66b_clock_module.edf

提示:根据您项目存放的实际位置,您可能会需要指定一个更长的路径。比如说,clock_module_i可能在aurora_64b66b_0_block_i/clock_module_i

7. 添加约束文件

在结果.edf文件的路径下,您将会在.srcs文件夹下找到您的约束文件.xdc。您需要将其添加到LabVIEW工程中,来约束您的IP核。

添加约束文件的时候,需要添加一些额外的修饰来使其能够在LabVIEW中使用。在Vivado中使用正常的约束文件,并不能保证在LabVIEW中也同样能正常使用。观察由LV FPGA工程编译产生的Xilinx生成记录,确保没有无法应用的约束条件。

可以参考用户手册来了解如何在约束文件中使用%ClipInstancePath%,来使Vivado中使用的约束条件能够在LV FPGA设计流程中也同样适用。

8. 为IP核创建一个VHDL封装

到这一步,IP核已经准备好,能够通过VHDL进行封装,作为6591R/92R的一个部件级IP核。

这个过程并不简单,需要对数字设计有较深的理解和较好的经验。这个也需要能够较好的理解由6591R/92R 提供的FPGA接口,并且能够合理地将这些接口应用到IP核以及封装部件上。

参考一个预先编译好的工程,可以获得关于CLIP工程中需要的工作有更好的理解。

关于这个过程的更多信息,可以参考用户手册。

9. 综合整个工程

当你生成了.edf和.xdc文件后,加上集成进CLIP的HDL源文件,您能够进一步到LabVIEW中将工程移植到6591R/92R中。在移植之前最后一个建议的步骤,就是先在这里综合并调试您的设计,来保证它能够正常运行。

在这个场景中,想要测试这个IP核和封装的正确性,一个VHDL测试文件是非常有必要的。Xilinx提供了一些带有仿真文件的范例程序,您可以通过了解它们继而为您自己的设计创建仿真文件。

对CLIP有一个更深的了解,可以帮助您更好地调试您的工程,以及更好地进行LV FPGA开发。通过这种方法,编译后的bit文件如果出现问题,也可以很好的进行调试。

10. 创建LabVIEW工程

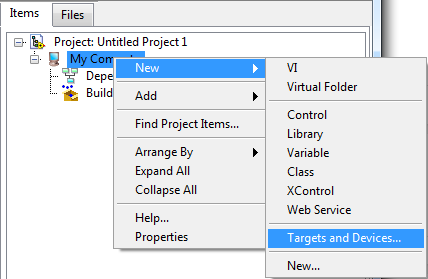

打开LabVIEW2014(或更新),创建一个新的工程。可以右击我的电脑,选择新建>>目标和设备来添加6591R/92R FPGA设备到工程中。

关于这个过程可以参考用户手册。

11. 添加CLIP到项目中

在目标设备配置好以后,就可以将您的经过VHDL封装的IP核添加到LabVIEW工程中,这样您就可以基于之前封装编译好的设计来获取CLIP的接口。右击FPGA目标,选择属性,会弹出一个新的配置窗口。

接下来添加CLIP到您的项目中,在左侧的区域中选择Component-Level IP选项,在右上角点击“创建”,这就会启动CLIP向导。根据下面的步骤来为您的工程创建封装的CLIP。

这里有个重要的提示,在您添加源文件到CLIP中时,您可能需要添加顶层的CLIP文件,CLIP所有用到的HDL文件,IP核的.edf网表文件,VHDL封装的.xdc约束文件。就Aurora范例项目来看:

参考用户手册获取更多关于这个步骤的更多信息。

12. 成功编译LV FPGA工程

到了这一步,已经几乎要完成了!假设CLIP的综合在Vivado中已经成功完成,继续在LabVIEW中融合一个新的生成规范来进行CLIP+LV FPGA的联合编译。如果约束文件也顺利完成实现,也就是说项目中没有时间冲突,同时没有其他的问题,那么您将最终获得6591R/92R的bit文件。

从LV FPGA侧传输数据到Host端可能会花费一些时间,并且配置CLIP和使用与IP核有关的标准化接口也会花费一些时间。我们提供了很多仪器设计库(IDL)来帮助您建立从CLIP接口到Host端的连接。

恭喜您!您成功从第三方获取了IP核并进行配置、生成,并将这个IP核集成到了6591R/92R应用中去。

相关链接:

White Paper: An Introduction to NI High-Speed Serial Instruments

Products and Services: NI PXIe-6591R

Products and Services: NI PXIe-6592R

NI PXIe-6591R Getting Started Guide

NI PXIe-6592R Getting Started Guide

Products and Services: NI PXIe-6591R

Products and Services: NI PXIe-6592R

NI PXIe-6591R Getting Started Guide

NI PXIe-6592R Getting Started Guide

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 11/07/2014

最近更新: 09/29/2015

文档编号: 6R6EOLM3