複数クロック領域でのFIFOについて

使用ソフトウェア: LabVIEW Development Systems>>LabVIEW Professional Development System

使用ソフトウェア・バージョン: 1.0

使用ソフトウェア・バージョンに特化: N/A

二次のソフトウェア: LabVIEW Modules>>LabVIEW FPGA Module

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

問題:

複数のタイミングループを使用し、DMA FIFOを用いてデータの送受信を行いたいと考えています。このときタイミングループのクロックソースはそれぞれのループで異なるものを使用できるのでしょうか。

解決策:

複数のクロックソースを使用してタイミングループを構築している場合、DMA FIFOの扱いには注意が必要です。DMA FIFOには以下の3つのオプションがあります。

- フリップフロップ

- ルックアップテーブル

- ブロックメモリ

各オプションの違いについては、一般ページ(FIFOプロパティダイアログボックス)をご覧ください。

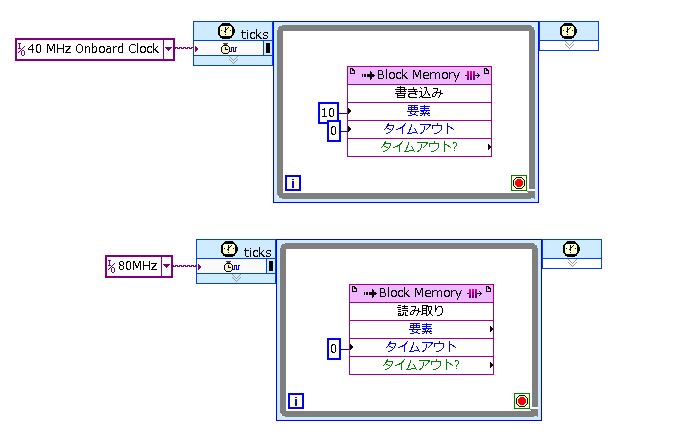

上記資料にも記載がありますが、異なるタイミング間でのFIFOは、ブロックメモリ以外ではコンパイル時のエラーが発生します。例えば下記のVIをコンパイルすると、ブロックメモリの場合問題なくコンパイルが可能です。

フリップフロップ、ルックアップテーブルを使用した場合、下記のエラーがコンパイル時に発生します。

「ターゲット指定」FIFOは「フリップフロップ」実装を使用するように構成されていますが、

別々のクロック領域で読み取りインタフェースと書き込みインタフェースを使用しています。

異なるクロック領域間で読み取りおよび書き込みを行う場合は、

「ターゲット指定」FIFOのFIFOプロパティダイアログで実装プルダウンメニューから「ブロックメモリ」を選択します。

そのため、FIFOを用いて異なるタイミングが使用されたタイミングループ間でデータを受け渡す場合、ブロックメモリを使用してください。

関連リンク:

添付:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

報告日時: 05/13/2015

最終更新日: 05/13/2015

ドキュメントID: 6XCIGPKL