4461采样率和更新率的设置

硬件: Modular Instruments>>Dynamic Signal Acquisition and Analysis (DSA)>>PXI-4461

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

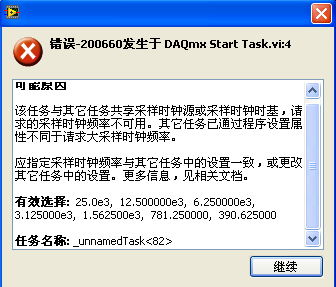

当我使用4461同步模拟采集和输出,运行DAQmx中的范例程序Multi-Function-Synch AI-AO Folder.vi时正常。但当我改变其中模拟采集的采样率或模拟输出的更新率时,程序报错,错误号200660,如图所示。

解答:

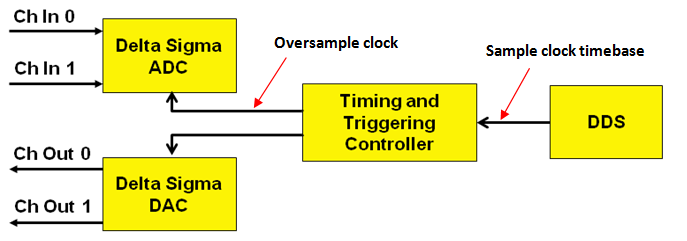

这是由于4461的采集和输出共享了同一个采样时钟时基(Sample clock timebase)引起的。DSA板卡如4461,其时钟机制如下图所示。

4461采用的是Delta-Sigma 类型的ADC和DAC,采集和输出时需要的是过采样时钟(Oversample clock)。过采样率和实际采样率或更新率呈一定的倍数关系,如下:

1.0kS/s≤fs≤51.2kS/s ………………128 fs

51.2kS/s≤fs≤102.4kS/s ………………64 fs

102.4kS/s≤fs≤204.8kS/s ………………128 fs

过采样时钟由Sample clock timebase分频而来,且Sample clock timebase的频率和设置的采样率或更新率有关,两者的关系可以参考表1。而Sample clock timebase则是由DDS根据板载高精度晶振和频率控制字直接数字合成而来。

假设ADC采样率设置为1kHz,则过采样率为128kHz,由DDS输出的采样时钟时基的频率为16384kHz,实际的频率值可能会由于晶振精度和DDS数字位数的影响而有细微偏差。

表1.采用率和采样时钟时基频率的关系

|

Sample Rate(fs)

|

Sample Clock Timebase Rate

|

|

|

Low-Frequency Alias Rejection Enabled

|

Low-Frequency Alias Rejection Disabled

|

|

|

1.0kS/s≤fs≤1.6kS/s

|

16,384 fs

|

512fs

|

|

1.6kS/s<fs≤3.2kS/s

|

8,192 fs

|

|

|

3.2kS/s<fs≤6.4kS/s

|

4,096 fs

|

|

|

6.4kS/s<fs≤12.8kS/s

|

2,048 fs

|

|

|

12.8kS/s<fs≤25.6kS/s

|

1,024 fs

|

|

|

25.6kS/s<fs≤51.2kS/s

|

512 fs

|

|

|

51.2kS/s<fs≤102.4kS/s

|

256 fs

|

256 fs

|

|

102.4kS/s<fs≤204.8kS/s

|

128 fs

|

128 fs

|

当同时运行4461上的模拟输入和模拟输出任务时,虽然可以为模拟输入和模拟输出设置不同的采样率。但是由于模拟输入和输出的过采样时钟都是由同一个Sample Clock Timebase分频而来,因此两者之间需满足一定的关系,即采样率和更新率的比为2的指数次方,同时需满足大于1kHz,小于204.8kHz。比如采样率为50kHz,则更新率可以是50kHz、100kHz、200kHz、25kHz,12.5kHz,但不能是40kHz。

另外,当同步多块板卡时,每块板卡上的采样率也需满足一定条件。当使用参考时钟同步多块板卡时,每块板卡上的采用率需满足2的指数次方关系,类似上述一块板卡AI和AO采样率的关系。当使用主从模式同步多块板卡时,即将主设备的采样时钟时基导入到从设备时,各板卡上的采样率除满足2的指数次方关系外,从设备的采样率还不能高于主设备的采样率。

相关链接:

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 03/29/2012

最近更新: 08/08/2012

文档编号: 5VS3JQ0M