使用NI VeriStand配置FPGA功能

硬件: Reconfigurable I/O (RIO)>>R Series>>PXI-7851R

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

本文主要介绍了用户如何在NI VeriStand环境中进行基于FPGA的相关配置。并以使用7851R输出PWM波为例,叙述了在VeriStand 2011运行环境中所需要的所有工作。

解答:

准备工作

NI VeriStand是一个基于配置的实时测试软件,它拥有与labVIEW类似的前面板,但无需任何编程工作。用户可以使用labVIEW、matlab等其他软件生成的模型文件导入VeriStand,方便快捷的实现硬件在环等实时测试应用。

与配置采集卡相比,对FPGA设备的配置流程会有所不同。接下来我们就以使用PCIe-7851R输出PWM波为例,叙述具体的配置流程。

NI VeriStand FPGA I/O接口工具

该接口工具提供了实现FPGA自定义I/O的labVIEW模板程序。

2) 安装完成后,在windows的共享文件夹下找到FPGA I/O特性的labVIEW模板。在win7系统中,该模板位于C:\Users\Public\Documents\National Instruments\NI VeriStand 2011\FPGA\Templates

这里我们选择NI VeriStand FPGA IO PXI-7831R模板项目。打开模板,我们会惊喜的发现,它已经为我们定义好了定时、触发、AIO、DIO、PWM、DMA读写这些常用的功能接口。

这里简单的对模板中PWM功能做一个说明:

1. 从8个数字口中读取PWM波,并分析出高电平与低电平的持续时间(以40MHz时钟滴答为单位)。

2. 将得到的高电平与低电平持续时间通过FIFO传输,控制另8个数字口的PWM波输出。

3) 由于这里我们希望通过在VeriStand中设置相应的高低电平时间来改变PWM波的占空比,因此对模板做以下修改,将反馈节点的输出断开。运行程序,生成FPGA比特文件。

FPGA 配置文件

现在我们已经有了FPGA的比特文件了,如何在VeriStand中实现对该比特文件的部署呢?在VeriStand中,XML格式的FPGA配置文件充当了这样一个比特文件“解读器”的角色。要自己创建一个配置文件不是一个简单的事情,但可以直接打开已有的一些配置,进行修改。这些配置文件存放路径为:C:\Users\Public\Documents\National Instruments\NI VeriStand 2011\FPGA\

打开PCIe-7851R Analog, PWM, Digital Ports,可以看到一个FPGA的配置文件大体结构为:

<FPGADMAChannelData>

<Bitfile>PXI-7851R.lvbitx</Bitfile>

<Categories>

…

</Categories>

<DMA_Read>

…

</DMA_Read>

<DMA_Write>

…

</DMA_Write>

</FPGADMAChannelData>

配置文件中各标签的含义,可以参考

仍在该路径下,将该配置文件另存一下,如改名PWM OUT。将<Bitfile>PXI-7851R.lvbitx</Bitfile>改为之前生成的比特文件的名字。并将比特文件复制到该路径下。

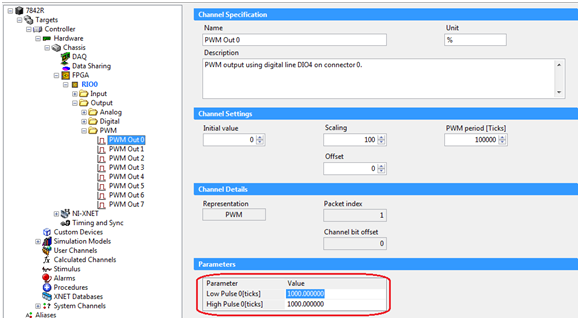

在<DMA_Write>标签下找到PWM Out 0,并为其添加两个参数来设定高低电平持续时间:

<PWM>

<Name>PWM Out 0</Name>

<Description>PWM output using digital line DIO4 on connector 0.</Description>

<Category>Output\PWM</Category>

<Scale>100</Scale>

<Unit>%</Unit>

<Symbol>PWM Out</Symbol>

<Parameters>

<U32>

<Name>Low Pulse 0[ticks]</Name>

<ControlName>_Low Pulse 0</ControlName>

<InitialValue>1000</InitialValue>

</U32>

<U32>

<Name>High Pulse 0[ticks]</Name>

<ControlName>_High Pulse 0</ControlName>

<InitialValue>1000</InitialValue>

</U32>

</Parameters>

</PWM>

需要注意的是,<ControlName>中的名字一定要与FPGA中相应控件的名字相同。这里使用的初始值为1000, (1/40M)*1000=25us,即PWM初始的设置为周期50us,占空比0.5。

VeriStand系统配置

经过之前一系列的准备工作,我们终于可以在VeriStand对FPGA进行配置运行了。

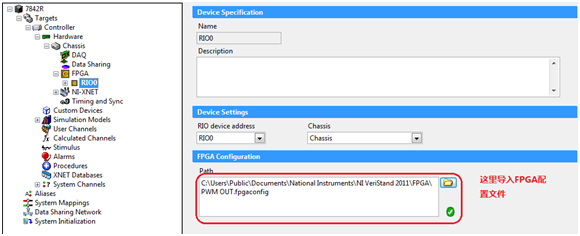

进入VeriStand系统浏览器,在FPGA目标中导入配置文件。

选中PWM out 0,在右边的配置页面中可以看到我们添加的两个参数Low Pulse和High Pulse,设置好我们需要的值,就可以在项目浏览器中运行测试了。

后记

至此我们已经完成了VeriStand基于FPGA I/O的调用。遗憾的是,通过这种方法并不能在测试运行时实时的改变参数,好在大多数PWM应用都会做成闭环控制。

VeriStand可以通过自定义设备(Custom Device)实现更加灵活的I/O配置,但同样,实现方式也更加复杂。

相关链接: 参考链接:为NI VeriStand创建基于FPGA的I/O特性

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 01/05/2013

最近更新: 01/05/2013

文档编号: 6541QPIZ