NI-TIO와 DAQ STC 카운터를 위한 온보드 메모리는 얼마나 큰가?

하드웨어: Counter/Timers (TIO)

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

문제점: NI-TIO와 DAQ STC 카운터를 위한 온보드 메모리는 얼마나 큰가?

솔루션:

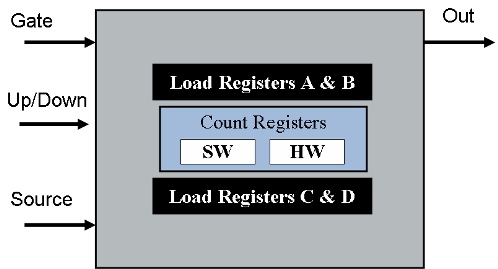

일반적으로 카운터는 현재의 카운트를 저장하기위해 하나의 카운트 레지스터를 사용한다. 소스 입력에서 에지가 검출될때, 카운트가 증가 또는 감소한다. NI-TIO와 DAQ STC 카운터는 카운터당 소프트웨어(SW)와 하드웨어(HW) 두개의 카운터 레지스터를 가지고 있다. 이는 아래의 그림과 같다.

소프트웨어 레지스터는 하드웨어 레지스터의 복사본이다. 즉, 카운터가 수행되는 동안, HW 레지스터의 인터럽트 없이 소프트웨어 어플리케이션에 의해 SW 레지스터가 쿼리될 수 있다는 것을 의미한다. 고속 버퍼 수행에의한 NI-TIO 카운터의 값은 최고 전송율로 SW와 HW 레지스터로부터 소프트웨어 버퍼로 교대로 래치된다. 실제로 이것은 각 카운터마다 두개의 샘플 FIFO를 만들게 된다. 더 큰 온보드 FIFO를 가진 디바이스를 사용하게되면 수행 능력을 향상 시킬 수 있다. 이는 KB 40TFKJ46: Benchmarks for Buffered Counter Input with M-Series Devices 에서 확인할 수 있으며 관련 링크는 아래와 같다.

관련 링크: KB 2HLA5TXA: Buffered Counter Operations with Counter Boards

KB 2JCD04EW: How are Buffers Read in Finite vs. Continuous Buffer Mode for Counter Operations?

KB 2C69GDQO: At What Signal Rates Can the Data Acquisition DAQ-STC Counter Chip Acquire?

KB 40TFKJ46: Benchmarks for Buffered Counter Input with M-Series Devices

Developer Zone: Counter/Timer Hardware Product-Feature Matrix

Products and Services: Counter/Timers

Product Manuals: DAQ-STC Technical Reference Manual

첨부:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

리포트 날짜: 08/03/2007

마지막 업데이트: 08/06/2007

문서 번호: 4C2E1H84