我如何把第三方的FPGA IP导入到一个LabVIEW Communication FPGA VI 中?

主要软件: LabVIEW Communications and System Design Suite

主要软件版本: 1.0

主要软件修正版本: N/A

次要软件: N/A

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

问题:

我有一个已经存在的第三方FPGA IP(VHDL,Verilog,netlist等等),我想把它导入到我的LabVIEW Communication应用的FPGA中。这是否可能?假如可能,应该如何做?

解答:

LabVIEW Communication使用IEEE标准的IP-XACT(IEEE 1685-2009)作为封装的基础,在工具链中进行IP核的整合和复用。IP-XACT XML架构一般在多种定义了端口分类和高级数据类型的XML扩展中使用。这种文件在LabVIEW Communication中会被识别为一个外部IP文件(.eip)

LabVIEW Communication的1.0版本并没有包含自动从第三方IP中生成EIP文件的功能。整合第三方IP的功能会在日后的版本中加入。

假如你需要整合一个第三方的FPGA IP到LabVIEW Communication中,你需要手动为你的IP创建一个EIP文件。手动创建一个EIP文件需要对IP-XACT XML架构有深入的了解。EIP架构是IP-XACT架构的一个扩展。

需要LabVIEW Communication整合第三方IP核功能的客户,可以使用下面的知识库文章中的范例程序用作参考。这个范例程序展示了一个供VHDL模型用的完整的EIP文件,它可以让你在手动生成EIP文件时得到一个基本的XML的认识。LabVIEW Communication 1.0不允许识别一个VHDL仿真模型,然而任何被EIP文件识别的VHDL都能用于Xilinx Xelab的仿真。

关于EIP文件的更多范例能在随LabVIEW Communication附送的PC(或者PXIe)的USRP-RIO Streaming范例中找到。

符合EIP架构的文件可以使用SystemDesigner中的FPGA终端导入到LabVIEW Communication中。

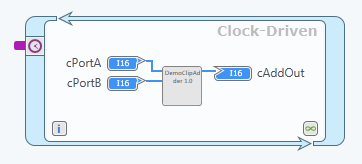

当EIP文件被添加到你的FPGA终端的reference container后,你可以你的IP添加到源代码的程序框图中。

相关链接: IEEE: 1685-2009 - IEEE Standard for IP-XACT

附件:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

报告日期: 04/02/2015

最近更新: 05/25/2015

文档编号: 6W1FR85Y